���>>��˾��B>>�yԇ�ļ�

�֙C��13401017970

�]�䣺lxtest@www.j44488.com

�Ԓ��+86-10-8200-3193

+86-10-8200-3199

+86-10-8200-3186

���棺+86-10-8200-5988

�]����100088

��ַ�������к���^�����h��·31̖

̩˼�ش�B1̖��

MOSFET��IGBT��늺ɜyԇ������B

����܊

��������о̩˼�yԇ���g����˾��������100088��

ժҪ��

����MOSFET�cIGBT�ѽ��ɞ鹦�ʰ댧�w�����е���Ҫ��������MOSFET��IGBT��늺ɜyԇ�������_�Ñ��Ѿá������r�І�λ�������P�����о������˸��õر��ϮaƷ�|�������ľ�MOSFET��IGBT��늺ɜyԇ�����M���˽�B��

�P�I�~��MOSFET��IGBT����늺�

���ڹ���MOSFET�cIGBT���Ќ�ͨ��裨늉����͡�����늉��ߡ��Ӻ��ε����c��Ŀǰ�ѽ��ɞ鹦�ʰ댧�w�������������е���Ҫ�������V��������Ӌ��C���O���Դ(AC/DC��DC/DC��DC/AC׃�Q��)���֙C����܇��ӡ�����·���x���x�����I�������������д�MOSFET��IGBT��̎���_�P��B�����_ʹ���@Щ��������������ʧЧ�İl��������Ҫ���Ⲣ����MOSFET��IGBT�����ԡ�����MOSFET�Ѓɂ���Ҫ�ą�����һ���nj�ͨ���RDS(on)����һ�����ǖ�늺�Qg�����H��ͨ�� FOM = Qg * Ron ���郞ֵ����������MOSFET���������ܣ�

��˖�늺ɺ͌�ͨ�����зdz���Ҫ������[1]����ͨ�����һ���o�Bֱ�����������^���לy��������늺ɵĜy��������Դ�͜yԇ�·��Ҫ���^�ߣ������e�DZ��y����ؓ�d���^�������ŘO늺ɵ����Բ����_�y�����P��Ҫ�����Č���BMOSFET��늺ɵ����P�������Y����܊��MIL-STD-750E 3471.2 ��B��늺ɵĜyԇ�������Լ��yԇ�Б�ע��Ć��}��IGBT�ĖŘO늺����Լ��yԇ�����cMOSFET��ͬ��ֻ�茢MOSFET�е�©�OD��Դ�OS��Q�鼯늘OC�Ͱl��OE���ɡ�

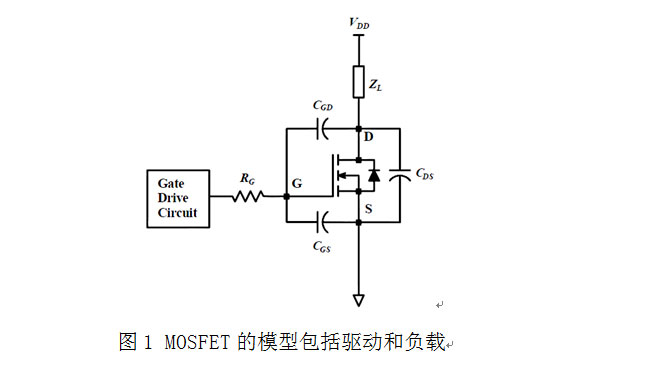

�D1��ʾ��һ����Ҋ��MOSFET����������ģ�ͣ�����߀���������·�����ĖŘO����Լ�©�O��һ��ؓ�d�迹���������փԽo����ݔ����ݣ�Ciss����ݔ����ݣ�Coss���ͷ�����ݣ�Crss�����D1�е�������ݷքe���x���£�

Ciss = Cgs + Cgd �� Coss = Cds + Cgd �� Crss = Cgd

���Ж�©���Cgd Ҳ�Q��������ݣ��ǖ�©늉��ķǾ��Ժ������o�B�µĖ�©��ݱȖ�Դ���С�ö࣬���S��©Դ늉�VDS��׃������©��ݿ���������Դ��ݵ�20��[2]����˖�©���Cgd����늺ɵ�Ӱ����

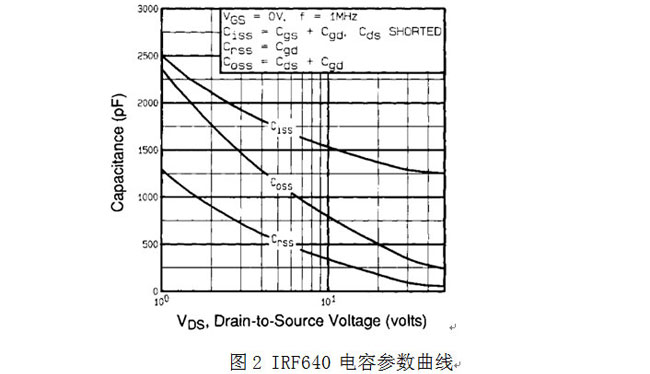

�D2��ʾ��ȡ��IRF640����݅��������������D�п��Կ����@Щ��݅����cVDS���P��Cgd��������݅����еĹ�ͬ׃������˿��������Ciss��Coss��Crss�����SVDS�ĸ�׃������Cgd�cCds�SVDS׃����ɵģ������փ��нo���Ė�늺Ʌ��������ض��l���µĜyԇ�Y������һ��������Cgs�Ǻ㶨�ġ�

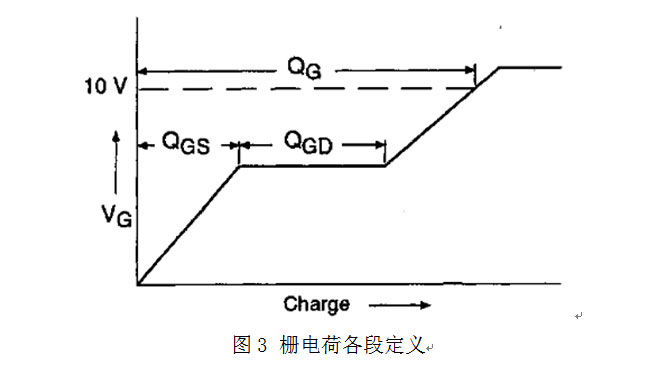

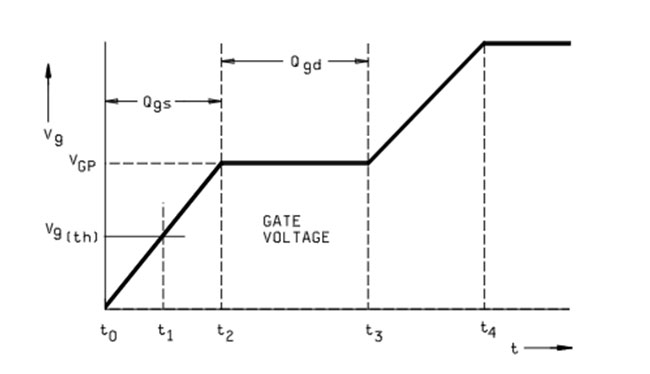

��늺�һ���������������ɣ�Qg�ǖŘO��늺ɣ�Qgs�ǖ�Դ늺ɣ�Qgd�ǖ�©늺ɣ�Ҳ������Ч��늺ɡ��D3��ʾ��IRF640�����փ��ϵĖ�늺��������x���������п��Կ�����Qgs��ʼ�c0�c����һ�����c��늺ɣ�Qgd��늺ɏĵ�һ�����c���ڶ������c��늺ɣ�Qg�Ǐ�0�c��VGS�����ӷ�ֵ늉�̎��늺ɡ������Џĵ�һ�����c���ڶ����c̎��������һ�lƽ��ֱ�����Q��ƽ�_������

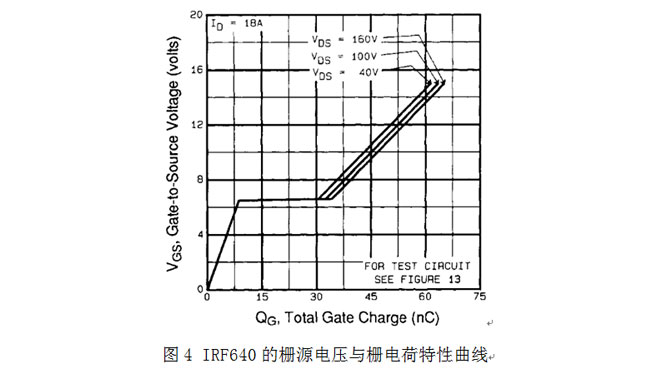

�D4��IRF640�����փԖŘO늉��ں����ӕr�����������������@ʾ�ˮ��㶨������������ŘO�ŘO늉�VGS�Ĵ�С�cע�뵽�ŘO��늺ɵ��Pϵ���D�п��Կ���VDS���ږ�늺����������е�ƽ�_�A�ξ��е�Ӱ푡�

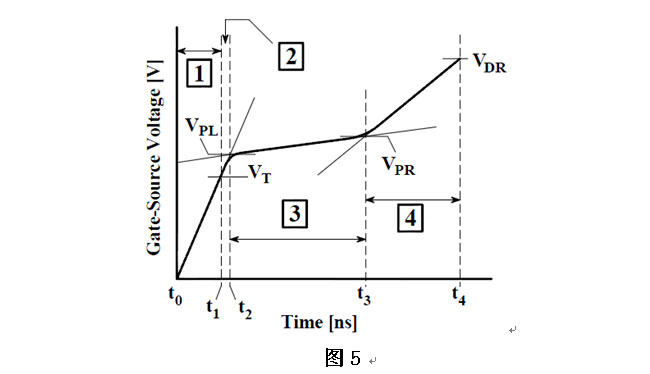

�D4�ǖ�Դ늉��c��늺��������c֮�����Ė�Դ늉��c��늕r�g������D5��ʾ���ڜyԇ��늺ɕr�����ږŘOʩ��һ������Դ�Դ_���ж���늺�ע�뵽�����ŘO������������x��ÿ���ͨ�^���w�����늺�������˖�늺ɿ���ͨ�^���r�g�e����ģ�

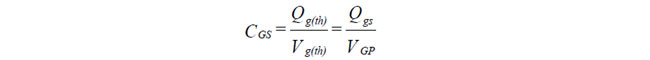

���ŘO����㶨�r����ʽ�ɺ�����

��ˣ����D1�еĖŘO�Ӟ�һ������Դ�r���Ϳ��Ԍ���Դ늉��c�r�g����������ͬ��Դ늉��c늺ɵ������������������õ�������ʽ��

Qg = Ig * t

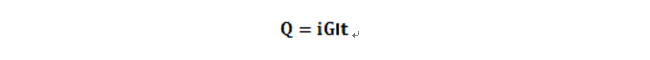

�D5������1~4����̖��ʾ��Դ늉�VGS�����^���д����Ă��A�Ρ��mȻ�����փ��нo�����������A�Σ������D5�֞��Ă�����A�θ����ڷ���:

��һ�A�Σ�

�ڵ�һ�A�Σ���Դ늉�VGS��0�c�������_��늉�VT��©�O���ID�]�����ӣ�©Դ늉�VDS��׃���˕r����̎���P���B����t0�r�̣��������ŘOʩ�Ӻ���Դ��VGS�_ʼ�������Ҍ��������Cgd��Cgs��늡���һ�A�������J��H��Cgs��늣�����VGS�����r��Cgs����Ҳ̎�ڳ�늠�B����VDS��׃�rCgs�cCgd��ȴ��S�࣬��˕��и��������Cgs��늡�������Ҫע����ǣ�Cgs���c늉��o�P�ļ�������������Cgd��Cds���c�����ɶ�늉������P����©�O늉����ږŘO늉��rCgd�cCds�c��݃ɶˉ���ɷ����Pϵ�������ŘO�c©�O늉����ߕr��Cgd���p�٣���©�O�cԴ�O늉����ߕrCdsҲ���p�١���VDS>VGS�ǣ����VGS���ߣ��t�����VGD�p�٣���˕�����Cgd���ߡ�Ҳ�����f����VGS���ߕrCgd���ߡ���ˣ��S��VGS���ߣ���늺ɕ����p���ӡ�

�ڶ��A�Σ�

�ڵڶ��A�Σ���Դ늉�VGS���_��늉�VT������ƽ�_늉�VPL��©Դ늉�VDS�_ʼ�p�٣�©�O����_ʼ���ӡ���©�O����_ʼ���ӕr������©�������������Ė�Դ늉�VGS�Q���_��늉����D6��ʾ��t=t1�r�̣�ID�_ʼ���Ӳ���VDS�_ʼ���ͣ���t=t2�r�̕r���������F��һ�����c���ڵ�һ�A�Σ�����늺��۷e�������ں�����Դ���������Cgs��Cgd��늵Ŀ�Ч��������Cgd����VGD�Ĝp�����p���ӡ��ڵڶ��A�Σ�늺ɵ�׃���������S��Cgd��VGD�ij˷e׃�����@�����ڣ�����V����݃ɶ�늉��C����ֵ���D1��ʾVGD��׃����©�O���ID��©�O�迹ZL�Q����

�����D1��ʹ�����ؓ�d����늸�ؓ�d�r���ڵڶ��A�εĹ��c̎�������ܱ��CID����_�����©�O���ID���ڹ��c�҂��_��������yԇʹ�ú���Դؓ�d�r����������r�£����c̎��VPL������©�O����_�����ĕr�̡�

�����A��

©Դ늉�VGS��ƽ�_늉���Ҳ�Q������ƽ�_��VPL������VPR��ID���ڴ��^����ij�c�_�����ֵ��VDS��t3�r���_����Сֵ��������ȫ��ͨ����t2��t3�r�̵�QGD��ע�뵽�ŘO��늺������S��VGS�^�m������������VGSб��Ѹ���½���������ijЩ��r����б�ʕ����͵�0б�ʡ��@�r�������J��VGS�M��늉�ƽ�_�A�Σ��@һ�A�Ε����mt2��t3�r�g���D5��ʾ��ƽ�_�A�ε�늉�б�����ɏĖŘO�������Ŀ�늺����p����r�Q���ģ����@һ늺�����׃��ȡ�Q��Cgd�cVGD�ij˷e���c�ڵڶ��A�εķ�����rһ�ӣ����VDS�cCgd����������늺���Ѹ�ٽ��ͣ��@�r�͕��и���ĖŘO�������Cgd���m���@�ӵ�늺���׃����������ӵ�Cgs��늺����͕��p�٣��@�Ӿ͕����VGS��б�ʽ��ͣ����VGD*Cgd׃���������еĖŘO�������Ҫȥ�a���@�N׃���r���ŘO늉�б�ʾ͕���0б�ʡ�����ڌ��H�yԇ�^���У������l�F���ڳ����_�P�p�ĵ�MOSFET��ƽ�_늉�б�ʌ�����0б�ʣ�������Qg�����^���MOSFET�����Լ�IGBT��ƽ�_늉������F0б�ʡ�

��VDS���͕rCgd�����ӣ�VDS������ID*RDS(on)�r����ֹͣ���ͣ��˕r���_�������ĵڶ������cVPR���˕rt=t3��

�����A��

�ڵ����A�Σ�VGS��VPR������VDR��©�O����������©Դ늉�VDS������С���˕r��t0��t4�����^��õ�Qg����VDS���͵�ID*RDS(on)�r��VGS�����µ�б���������˕rVDS������׃�����к���Դ�ӵĖŘO������ٴν^������Cgs�����˕r�ŘO늉�����б�ʌ����ڵ�һ�A�����Եͣ��@�����ڴ˕rCgd�ѽ��S��VGD�Ľ��Ͷ�׃�����S�࣬�����cCgs���������ֵ�ӽ����ŘO�����ͬ�r��Cgs��Cgd��늣�ԭ���c��һ�A����ͬ�������@��©�O늉����ږŘO늉������Cgs��Cgd���c늉��o�P��һ������

�ĈD6 ��������ؿ������ڹ������_�P��B�µ�MOSFET����t1֮ǰ��©�O늉���ߵ�©�O������ƞ��㣻��t3֮��©�O����_����˕r��©�O늉��ֽ��ƞ��㣬�������@�ɂ��A�ε�����p��P���ƞ��㡣�书�ʓp�ļ�����t1��t2���_����t2��t3��ƽ�_�A�Σ�MOSFET���P���r�IJ����LjD6���R�p��ͬ�Ӽ������@�ɂ��A�Ρ���ͬ�ӵ��ӗl���£������Ė�늺�Խ��t1��t3�ĕr�g��Խ�L���������_�P�r�ēp�ľ�Խ����˖�늺Ɍ��ڹ������_�P��B�µ�MOSFET��һ���dz���Ҫ�ą�����

�e���{���LjD6����ʾ��©�O늉�VD ��©�O���ID �c��늺�׃���r�Č����Pϵ�����ø��ٺ���Դ��ؓ�d�r�ĽY��������������ؓ�d��©�O���ID��׃���������S©�O늉�VD׃�������Ķ�Ӱ�VGS��T2̎�IJ��κ�T2��T3��ƽ�_���֣�ֱ��Ӱ푖�늺ɵĜyԇ�Y����

��܊��MIL-STD-750E 3471.2�ж��x�Ė�늺ɜyԇ�ֽ�ĸ���Ԕ������늺ɜyԇ�����ֵĶ��x���£�

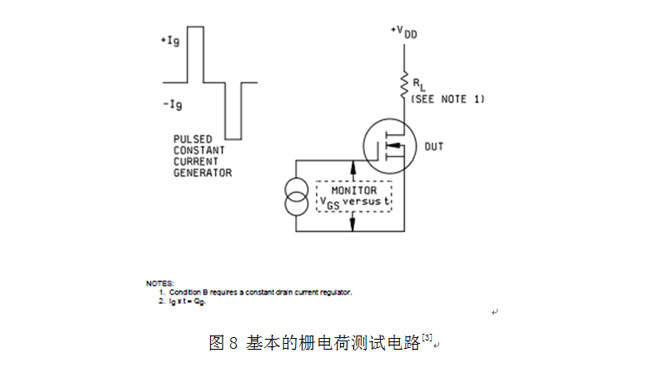

�D8 ����܊��MIL-STD-750E 3471.2�нo����N�ϵ�MOSFET��늺ɻ����yԇ�·���D�Q�ŘO����Դ�}�_��VDD�O�ԣ��Ϳ��Ԍ�P�ϵ�MOSFET�yԇ��

��܊���Ќ���늺ɜyԇ�·��©�Oؓ�d���˃ɷNҎ����

Condition A��Ҏ��©�Oʹ�����RL����ؓ�d�M�Мyԇ��

���ֵ��������ʽ�_����

RL = VDD / ID

���y������ֹ��B�r��©�O늉�VDD���O��������©Դ����늉���50%��80%֮�g��ͬ�rҎ��ID >= 100 mA ��

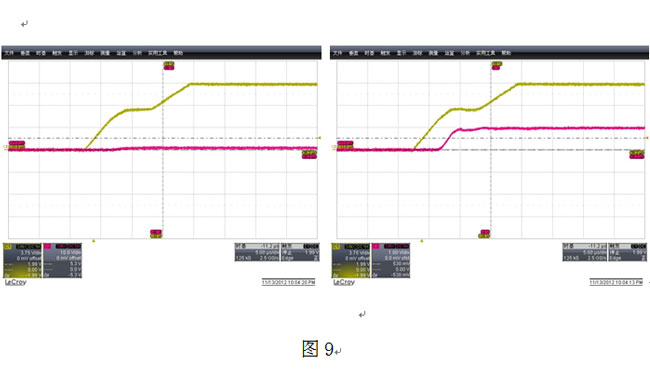

�@�N�yԇ�·�dz����Σ��������ڱ��y�����_�����P����^����ID����SVDS׃����ID����-©��ݵij�늵�׃����ʹVGS�������D5����t1��t2��һ���c̎�^�ڏ���׃�ÈA�����o���ʴ_�_�����c�ĕr�g���ˣ��Ķ�ֱ��Ӱ�Qgs��Qgd�Ĝy�����҂���LX9600��늺ɜyԇϵ�y[4]�����ˌ��Ȝyԇ���D9�е���D����ʹ�����ؓ�d�r��Vgs���Σ��Sɫ����

LX9600�y��©�O���ؓ�d����һ�����Դؓ�d���ң���Vgs���^

���y����IRF640

Condition B��©�ODʹ�ú���Դ��QRLؓ�d���yԇ�·���^���s����©�O����Դ��Ҫ��dz��ߡ�����Դ����Ǹ��ӵģ��ڱ��y������ͨ�r�ܳ���VDD�ĸ߉���늉������Ķ�ʮ����һǧ�����ң��ڱ��y������ֹ�r�зdz��͵�͉���������Ҫ�����@������Դ�ĄӑB푑���횷dz��죬푑��r�g���ͱ��y������푑��r�g������ͬ����t��Ӱ�Qgd�������������D5 ��t2-t3���֣����D9�е��҈D��һ�����ٺ���Դ��ؓ�d�rVgs���Sɫ�����������������@����t2-t3�A�ε�������ƽ̹�������е��䡣

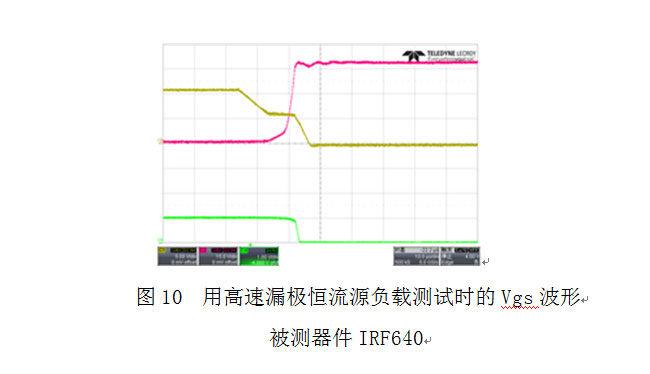

�D10�Dz��ø��ٺ���Դ����ؓ�d�r��Vgs�����������yԇ�Y���cIRF640�����փԽo���������������D2����ȫ�Ǻϡ�

�D3�͈D4��ʾ����MOSFET��ͨ�r�����������������P���r����ጷ�늺ɣ��@��һ���c��ͨ�෴���^�̣��mȻ���H�����Ќ�ͨ���P�����ʹ�ò�ͬ�����·�����ŘO늺Ɍ���Ӱ푡�ԭ�������c������ֵ����ͬ��

���MOSFET�_�����P���r�ĖŘO늺�����ȵģ������ڌ��H�yԇ��һ�����늉��}�_�_���������P��ķ���ȥ�y����늺ɣ��@�ӿ����·���^���Ρ����Ұ�ȫ�ɿ����D9�Dz����P���r�y���ĖŘO늉����Sɫ����©�O늉����tɫ����������Gɫ�����Σ����Կ���VGS�c�D8�еIJ������R��ġ�

��܊�˜yԇ�l��A��B���ŘO���Ig��Ҏ������ͬ�ģ�Ҫ��ŘO����Դ�ı��y�����P�ൽ��ͨ��ͨ���P����^�ȕr�g��s50uS ��Ig ���O��ֵ����оƬ�ߴ������������0.1mA �� 5mA ��

���`�Ќ���һЩ�����������e�rIGBT�M�������ɶ����������M�ɵģ���ݔ����ݷdz������Ig �O��ֵС�������±��y������t1��t3�A�Σ��D6���r�g�^�L��������Ѹ�ٰl�������p�ġ���ˑ����������փԽo����ݔ����ݵȅ�������ŘO����Դ��Igֵ����܊���н��h�ŘO����Դ�Д�ʮ������ݔ��������һ�㹤�����OӋһ��0.1mA��200mAݔ���Ŀɾ��̖ŘO����Դ�Ϳ��Ի����M��ȫ���yԇ����

������Ig�r������ݔ��ֲ���������Ҫ�Ǹп�����Ӱ푣���t��ʾ�������^�쵽��Vgs늉����ξͲ����挍��ӳ��늺ɵ�׃�����ڹ��̌��`�б����ҕ�ŘO����Դ�c���y����֮�g���B�ӺͲ��֡�

�oՓ����A��B�ǷN�y���l������܊���ж�Ҏ���yԇ�r�ܚ��ضȑ��� +25��C�����H�Ϝضȵ�׃������늺��@������Ӱ��^С���ɸ�����ͬ�����Ҏ���yԇ�r���ضȵ�Ҫ���Խ��͜yԇ�ɱ���

�yԇ�ø��ٔ��ִ惦ʾ�����Ď���������300M���ɘ����� >= 1G���������������ݔ��ͨ������ͬ�r�^��ŘO늉���©�O늉���©�O������Ρ�����©�O����IJɘӑ�ʹ�ø���������������ɘ��c��÷���Դ�O���Ա���©�Oһ�˵ķֲ�����������Ӱ푡�

�ŘO늉�ݔ��ͨ��̽�^��ǰ�ˑ��о��_�ӣ���܊���в��õ����\��Ŵ���CA3240E������S������ݔ���迹1.5T��ݔ�����10pA��ݔ�����4pF���@�ӿ��Խ���ʾ����̽�^������`�

�����īI��

���߽�B��

����܊�����¼����·���댧�w���������yԇ�����P���g�о���ϵ�y���_�l���ƹ�����ʮ���꣬���·��Ҷ������c���P�Ŀ�м����·�yԇϵ�y�аl���n�}��ؓ؟�ˣ��Г��^�����п�ί�ͱ����н���ί�Ķ����ش�����Ŀ���_�l�İ댧�w��������ֱ�������yԇϵ�yBC3193�������S�ң�܊��Ժ������У���I��õ��V�����á�Ŀǰ���Ƶİ댧�w���������yԇϵ�yLX9600,�yԇ���ݺ��w���r�g��������늺ɡ��Y��ݡ�ѩ������������֏͕r�g�Ƚ����������F�α����ԄӜyԇ���g�о����������̎��������пƌW���g�о�Ժ�댧�w���������yԇ��������Σ�������о̩˼�yԇ���g����˾�����̎���